# DS80C320/DS80C323 High-Speed/Low-Power Microcontrollers

#### www.maxim-ic.com

#### **FEATURES**

## ■ 80C32-Compatible

8051 Pin and Instruction Set Compatible Four 8-Bit I/O Ports Three 16-Bit Timer/Counters 256 Bytes Scratchpad RAM Addresses 64kB ROM and 64kB RAM

## High-Speed Architecture

4 Clocks/Machine Cycle (8032 = 12)

DC to 33MHz (DS80C320)

DC to 18MHz (DS80C323)

Single-Cycle Instruction in 121ns

Uses Less Power for Equivalent Work

Dual Data Pointer

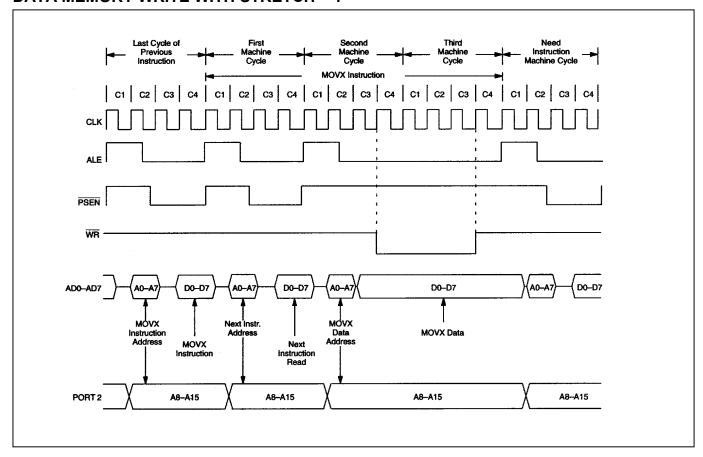

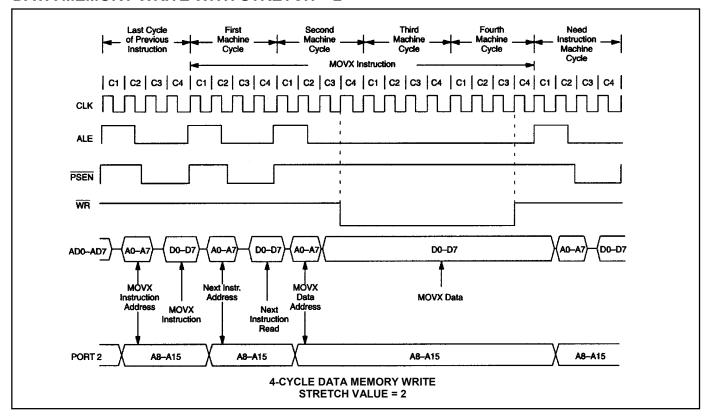

Optional Variable Length MOVX to Access

Fast/Slow RAM/Peripherals

## High-Integration Controller Includes:

Power-Fail Reset Programmable Watchdog Timer Early Warning Power-Fail Interrupt

- Two Full-Duplex Hardware Serial Ports

- 13 Total Interrupt Sources with Six External

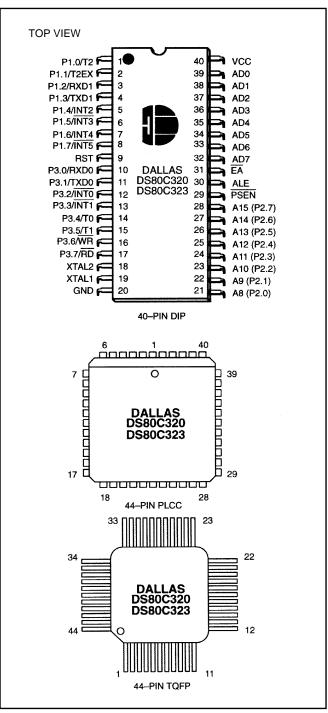

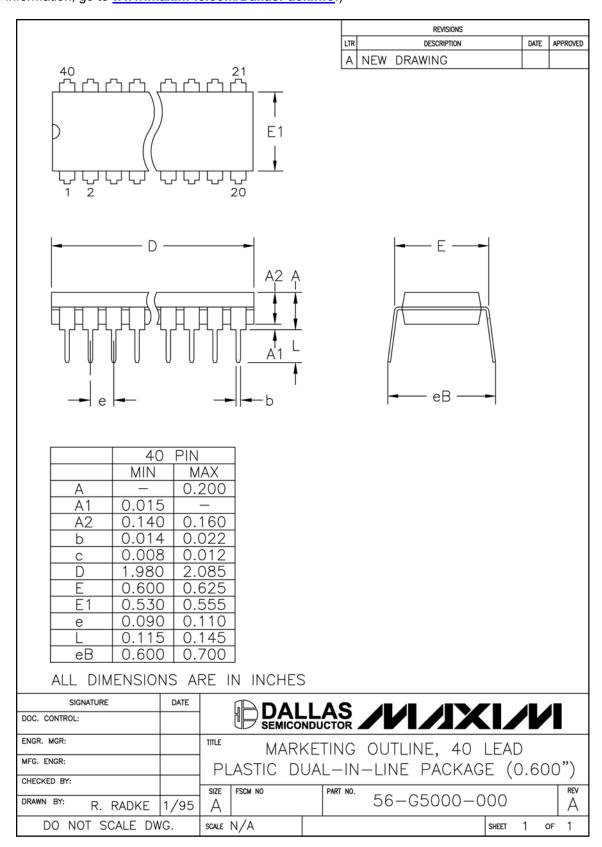

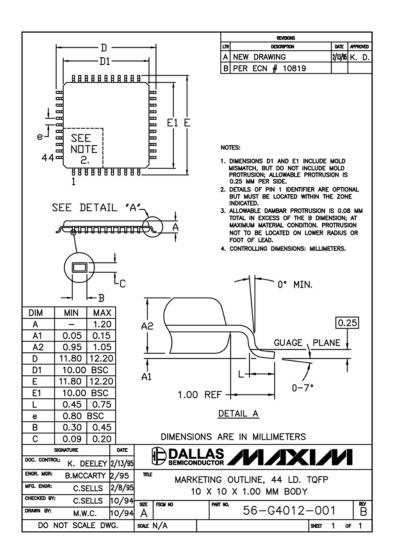

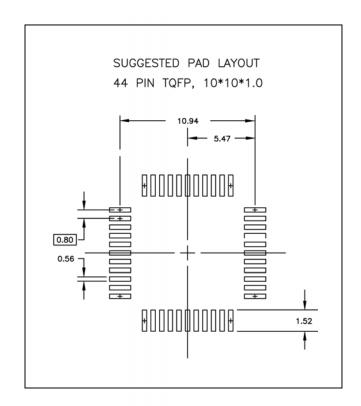

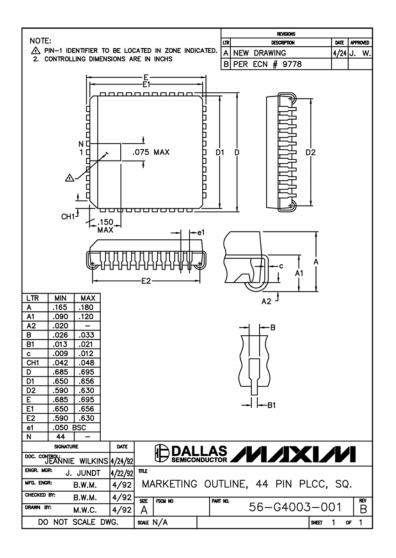

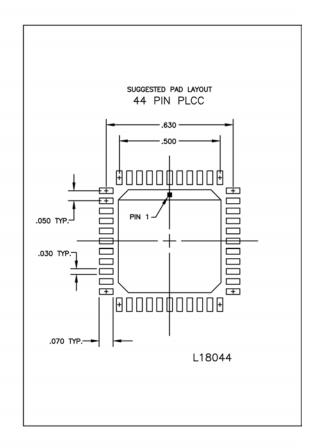

- Available in 40-Pin DIP, 44-Pin PLCC, and 44-Pin TQFP

The *High-Speed Microcontroller User's Guide* must be used in conjunction with this data sheet. **Download it** at: <a href="https://www.maxim-ic.com/microcontrollers">www.maxim-ic.com/microcontrollers</a>.

Data sheets contain pin descriptions, feature overviews, and electrical specifications, whereas the user's guide contains detailed information about device features and operation.

## PIN CONFIGURATIONS

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

1 of 40 REV: 101006

#### DETAILED DESCRIPTION

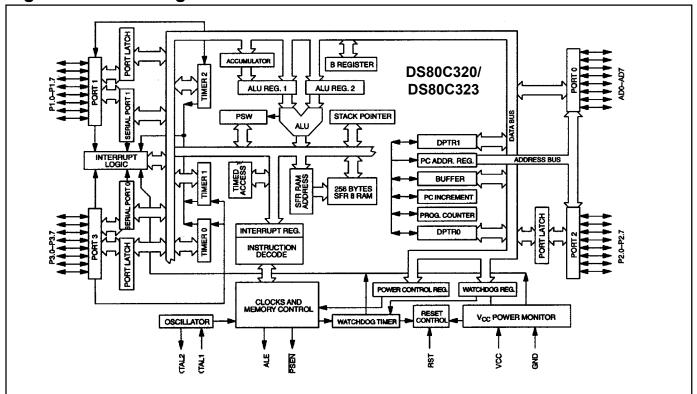

The DS80C320/DS80C323 are fast 80C31/80C32-compatible microcontrollers. Wasted clock and memory cycles have been removed using a redesigned processor core. As a result, every 8051 instruction is executed between 1.5 and 3 times faster than the original for the same crystal speed. Typical applications see a speed improvement of 2.5 times using the same code and same crystal. The DS80C320 offers a maximum crystal rate of 33MHz, resulting in apparent execution speeds of 82.5MHz (approximately 2.5X).

The DS80C320/DS80C323 are pin compatible with all three packages of the standard 80C32 and offer the same timer/counters, serial port, and I/O ports. In short, the devices are extremely familiar to 8051 users, but provide the speed of a 16-bit processor.

The DS80C320 provides several extras in addition to greater speed. These include a second full hardware serial port, seven additional interrupts, programmable watchdog timer, power-fail interrupt and reset. The device also provides dual data pointers (DPTRs) to speed block data memory moves. It can also adjust the speed of off-chip data memory access to between two and nine machine cycles for flexibility in selecting memory and peripherals.

The DS80C320 operating voltage ranges from 4.25V to 5.5V, making it ideal as a high-performance upgrade to existing 5V systems. For applications in which power consumption is critical, the DS80C323 offers the same feature set as the DS80C320, but with 2.7V to 5.5V operation.

Designers must have two documents to fully use all the features of this device: this data sheet and the *High-Speed Microcontroller User's Guide*, available on our website at <a href="https://www.maxim-ic.com/microcontrollers">www.maxim-ic.com/microcontrollers</a>. Data sheets contain pin descriptions, feature overviews, and electrical specifications, whereas our user's guides contain detailed information about device features and operation.

#### ORDERING INFORMATION

| PART         | Pb-FREE/RoHS-<br>COMPLIANT | TEMP RANGE                         | MAX CLOCK<br>SPEED (MHz) | PIN-PACKAGE    |

|--------------|----------------------------|------------------------------------|--------------------------|----------------|

| DS80C320-MCG | <b>DS80C320-</b> MCG+      | $0^{\circ}$ C to $+70^{\circ}$ C   | 25                       | 40 Plastic DIP |

| DS80C320-QCG | DS80C320-QCG+              | $0^{\circ}$ C to $+70^{\circ}$ C   | 25                       | 44 PLCC        |

| DS80C320-ECG | DS80C320-ECG+              | $0^{\circ}$ C to $+70^{\circ}$ C   | 25                       | 44 TQFP        |

| DS80C320-MNG | DS80C320-MNG+              | $-40^{\circ}$ C to $+85^{\circ}$ C | 25                       | 40 Plastic DIP |

| DS80C320-QNG | DS80C320-QNG+              | $-40^{\circ}$ C to $+85^{\circ}$ C | 25                       | 44 PLCC        |

| DS80C320-ENG | DS80C320-ENG+              | -40°C to +85°C                     | 25                       | 44 TQFP        |

| DS80C320-MCL | DS80C320-MCL+              | $0^{\circ}$ C to $+70^{\circ}$ C   | 33                       | 40 Plastic DIP |

| DS80C320-QCL | DS80C320-QCL+              | $0^{\circ}$ C to $+70^{\circ}$ C   | 33                       | 44 PLCC        |

| DS80C320-ECL | DS80C320-ECL+              | $0^{\circ}$ C to $+70^{\circ}$ C   | 33                       | 44 TQFP        |

| DS80C320-MNL | DS80C320-MNL+              | -40°C to +85°C                     | 33                       | 40 Plastic DIP |

| DS80C320-QNL | DS80C320-QNL+              | $-40^{\circ}$ C to $+85^{\circ}$ C | 33                       | 44 PLCC        |

| DS80C320-ENL | DS80C320-ENL+              | -40°C to +85°C                     | 33                       | 44 TQFP        |

| DS80C323-MCD | <b>DS80C323-</b> MCD+      | $0^{\circ}$ C to $+70^{\circ}$ C   | 18                       | 40 Plastic DIP |

| DS80C323-QCD | DS80C323-QCD+              | 0°C to +70°C                       | 18                       | 44 PLCC        |

| DS80C323-ECD | DS80C323-ECD+              | 0°C to +70°C                       | 18                       | 44 TQFP        |

| DS80C323-QND | DS80C323-QND+              | -40°C to +85°C                     | 18                       | 44 PLCC        |

| DS80C323-END | DS80C323-END+              | -40°C to +85°C                     | 18                       | 44 TQFP        |

<sup>+</sup> Denotes a Pb-free/RoHS-compliant device.

Figure 1. Block Diagram

## PIN DESCRIPTION

| THE DESCRIPTION |        |        |                 |                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------------|--------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 | PIN    |        | NAME            | EUNCTION                                                                                                                                                                                                                                                                                                                             |  |  |

| DIP             | PLCC   | TQFP   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                             |  |  |

| 40              | 44     | 38     | V <sub>CC</sub> | +5V (+3V for DS80C323)                                                                                                                                                                                                                                                                                                               |  |  |

| 20              | 22, 23 | 16, 17 | GND             | Digital Circuit Ground                                                                                                                                                                                                                                                                                                               |  |  |

| 9               | 10     | 4      | RST             | <b>Reset Input.</b> The RST input pin contains a Schmitt voltage input to recognize external active-high reset inputs. The pin also employs an internal pulldown resistor to allow for a combination of wired OR external reset sources. An RC is <i>not</i> required for power-up, as the device provides this function internally. |  |  |

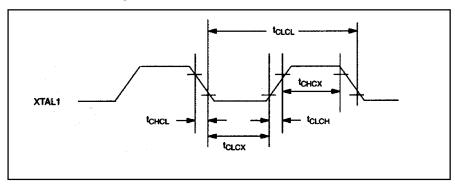

| 18              | 20     | 14     | XTAL2           | Crystal Oscillator Pins. XTAL1 and XTAL2 provide support for parallel-resonant, AT-cut crystals. XTAL1 acts also as an input in the                                                                                                                                                                                                  |  |  |

| 19              | 21     | 15     | XTAL1           | event that an external clock source is used in place of a crystal. XTAL2 serves as the output of the crystal amplifier.                                                                                                                                                                                                              |  |  |

| 29              | 32     | 26     | PSEN            | Program Store-Enable Output, Active Low. This signal is commonly connected to external ROM memory as a chip enable. PSEN provides an active-low pulse width of 2.25 XTAL1 cycles with a period of four XTAL1 cycles. PSEN is driven high when data memory (RAM) is being accessed through the bus and during a reset condition.      |  |  |

# **PIN DESCRIPTION (continued)**

|     | PIN  |        | NIAME     | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |            | INI        | INCTION   |                                                |  |

|-----|------|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------------|-----------|------------------------------------------------|--|

| DIP | PLCC | TQFP   | NAME      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            | FU         | UNCTION   |                                                |  |

| 30  | 33   | 27     | ALE       | Address Latch-Enable Output. This pin functions as a clock to latch the external address LSB from the multiplexed address/data bus. This signal is commonly connected to the latch enable of an external 373 family transparent latch. ALE has a pulse width of 1.5 XTAL1 cycles and a period of four XTAL1 cycles. ALE is forced high when the device is in a reset condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |            |           |                                                |  |

| 39  | 43   | 37     | AD0       | Dowt O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | T4          | /O44       | Dant O is  | . 41. 0   | d o dduogg/doto hyva                           |  |

| 38  | 42   | 36     | AD1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · •         |            |            |           | d address/data bus.                            |  |

| 37  | 41   | 35     | AD2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |            |           | a memory address is                            |  |

| 36  | 40   | 34     | AD3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |            |           | to a bi-directional data dread/write external  |  |

| 35  | 39   | 33     | AD4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |            |           | o true port latch and                          |  |

| 34  | 38   | 32     | AD5       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |            |           | et condition of Port 0 is                      |  |

| 33  | 37   | 31     | AD6       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            | ors are ne |           | ct condition of 1 oft o is                     |  |

| 32  | 36   | 30     | AD7       | ingn. i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vo punu     | ip resisio | ns are ne  | cucu.     |                                                |  |

|     |      |        |           | Port 1, I/O. Port 1 functions as both an 8-bit, bidirectional I/O port and an alternate functional interface for Timer 2 I/O, new External Interrupts, and new Serial Port 1. The reset condition of Port 1 is with all bits at logic 1. In this state, a weak pullup holds the port high. This condition also serves as an input mode, since any external circuit that writes to the port will overcome the weak pullup. When software writes a 0 to any port pin, the device will activate a strong pulldown that remains on until either a 1 is written or a reset occurs. Writing a 1 after the port has been at 0 will cause a strong transition driver to turn on, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again becomes the output high (and input) state. The alternate modes of Port 1 are outlined as follows: |             |            |            |           |                                                |  |

| 1–8 | 2–9  | 40–44, | P1.0–P1.7 | DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIN<br>PLCC | TQFP       | PORT       | ALTERNATE | FUNCTION                                       |  |

|     |      | 1–3    |           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2           | 40         | P1.0       | T2        | External I/O for Timer/Counter 2               |  |

|     |      |        |           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3           | 41         | P1.1       | T2EX      | Timer/Counter 2<br>Capture/Reload Trigger      |  |

|     |      |        |           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4           | 42         | P1.2       | RXD1      | Serial Port 1 Input                            |  |

|     |      |        |           | 4 5 43 P1.3 TXD1 Serial Port 1 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |            |            |           |                                                |  |

|     |      |        |           | 5 6 44 P1.4 INT2 External Interrupt 2 (Positive-Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |            |            |           |                                                |  |

|     |      |        |           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7           | 1          | P1.5       | ĪNT3      | External Interrupt 3 (Negative-Edge Detect)    |  |

|     |      |        |           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8           | 2          | P1.6       | INT4      | External Interrupt 4<br>(Positive-Edge Detect) |  |

|     |      |        |           | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9           | 3          | P1.7       | ĪNT5      | External Interrupt 5 (Negative-Edge Detect)    |  |

**PIN DESCRIPTION (continued)**

| PIN DESCRIPTION (CONTINUED) |               |                |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                       |                                     |

|-----------------------------|---------------|----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| DIP                         | PIN           | TOED           | NAME                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |       | I    | FUNCTION                                                                                                                                                                                                                                                              |                                     |

| 21                          | PLCC<br>24    | <b>TQFP</b> 18 | 4 9 (D2 0)               | D 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      | 4 D 4 | 2    | 4 MCD C                                                                                                                                                                                                                                                               | 4 1 11 '                            |

| 22                          | 25            | 19             | A8 (P2.0)<br>A9 (P2.1)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Port 2, Output</b> . Port 2 serves as the MSB for external addressing. P2.7 is A15 and P2.0 is A8. The device will automatically place the                                                        |       |      |                                                                                                                                                                                                                                                                       |                                     |

| 23                          | 26            | 20             | A9 (F2.1)<br>A10 (P2.2)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                       | and RAM access.                     |

| 24                          | 27            | 21             | A10 (12.2)               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                       | nary I/O port, the value            |

| 25                          | 28            | 22             | A11 (12.3)<br>A12 (P2.4) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                    |       |      |                                                                                                                                                                                                                                                                       | on the pins (due to                 |

| 26                          | 29            | 23             | A13 (P2.5)               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                       | 2 in software is only               |

| 27                          | 30            | 24             | A14 (P2.6)               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                       | MOVX @Ri, A. These                  |

| 28                          | 31            | 25             | A15 (P2.7)               | MSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | instructions use the Port 2 internal latch to supply the external address MSB. In this case, the Port 2 latch value will be supplied as the address information.                                     |       |      |                                                                                                                                                                                                                                                                       |                                     |

|                             |               |                |                          | Port 3, Input/Output. Port 3 functions as both an 8-bit, bidirectional I/O port and an alternate functional interface for External Interrupts, Serial Port 0, Timer 0 & 1 Inputs, RD and WR strobes. The reset condition of Port 3 is with all bits at logic 1. In this state, a weak pullup holds the port high. This condition also serves as an input mode, since any external circuit that writes to the port will overcome the weak pullup. When software writes a 0 to any port pin, the device will activate a strong pulldown that remains on until either a 1 is written or a reset occurs. Writing a 1 after the port has been at 0 will cause a strong transition driver to turn on, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again becomes both the output high and input state. The alternate modes of Port 3 are outlined below: |                                                                                                                                                                                                      |       |      | for External Interrupts,  R strobes. The reset In this state, a weak so serves as an input of the port will overcome of any port pin, the device on until either a 1 is e port has been at 0 will llowed by a weaker and driver turns off, the h and input state. The |                                     |

| 10.15                       | 11, 13–       |                |                          | DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PIN<br>PLCC                                                                                                                                                                                          | TQFP  | PORT | ALTERNATE                                                                                                                                                                                                                                                             | MODE                                |

| 10–17                       | 19            | 5, 7–13        | P3.0–P3.7                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11                                                                                                                                                                                                   | 5     | P3.0 | RXD0                                                                                                                                                                                                                                                                  | Serial Port 0 Input                 |

|                             |               |                |                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                                                                                                                                   | 7     | P3.1 | TXD0                                                                                                                                                                                                                                                                  | Serial Port 0 Output                |

|                             |               |                |                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14                                                                                                                                                                                                   | 8     | P3.2 | ĪNT0                                                                                                                                                                                                                                                                  | External Interrupt 0                |

|                             |               |                |                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                   | 9     | P3.3 | ĪNT1                                                                                                                                                                                                                                                                  | External Interrupt 1                |

|                             |               |                |                          | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16                                                                                                                                                                                                   | 10    | P3.4 | ТО                                                                                                                                                                                                                                                                    | Timer 0 External Input              |

|                             |               |                |                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17                                                                                                                                                                                                   | 11    | P3.5 | T1                                                                                                                                                                                                                                                                    | Timer 1 External Input              |

|                             |               |                |                          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18                                                                                                                                                                                                   | 12    | P3.6 | WR                                                                                                                                                                                                                                                                    | External Data Memory Write Strobe   |

|                             |               |                |                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                                                                                                                                                                   | 13    | P3.7 | RD                                                                                                                                                                                                                                                                    | External Data Memory Read<br>Strobe |

| 31                          | 35            | 29             | EA                       | External Access, Active-Low Input. This pin must be connected to ground for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |       |      |                                                                                                                                                                                                                                                                       |                                     |

| _                           | 12, 34,<br>1* | 6, 28,<br>39*  | N.C.                     | They a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No Connection (Reserved). These pins should not be connected. They are reserved for use with future devices in this family.  *These pins are reserved for additional ground pins on future products. |       |      |                                                                                                                                                                                                                                                                       |                                     |

## 80C32 COMPATIBILITY

The DS80C320/DS80C323 are CMOS 80C32-compatible microcontrollers designed for high performance. In most cases, the devices will drop into an existing 80C32 design to significantly improve the operation. Every effort has been made to keep the devices familiar to 8032 users, yet they have many new features. In general, software written for existing 80C32-based systems will work on the DS80C320 and DS80C323. The exception is critical timing, because the high-speed microcontroller performs its instructions much faster than the original. It may be necessary to use memories with faster access times if the same crystal frequency is used.

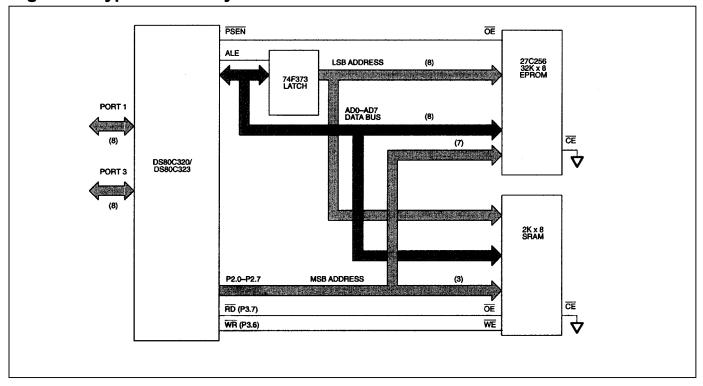

Application Note 57: DS80C320 Memory Interface Timing is a useful tool to help the embedded system designer select the proper memories for her or his application.

The DS80C320/DS80C323 run the standard 8051 instruction set and is pin compatible with an 80C32 in any of three standard packages. They also provide the same timer/counter resources, full-duplex serial port, 256 bytes of scratchpad RAM, and I/O ports as the standard 80C32. Timers will default to a 12 clock-per-cycle operation to keep timing compatible with original 8051 systems. However, they can be programmed to run at the new 4 clocks per cycle if desired.

New hardware features are accessed using special-function registers that do not overlap with standard 80C32 locations. A summary of these SFRs is provided below.

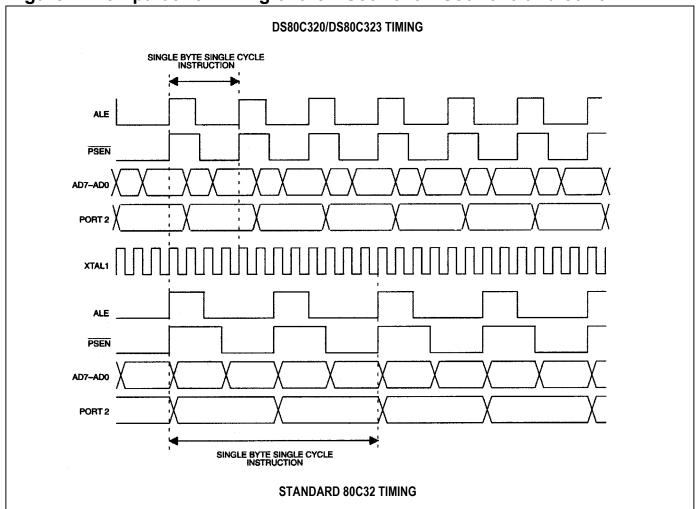

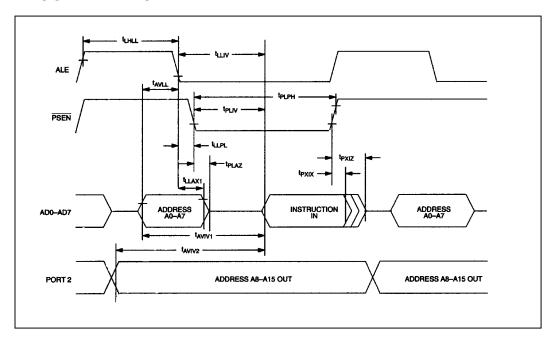

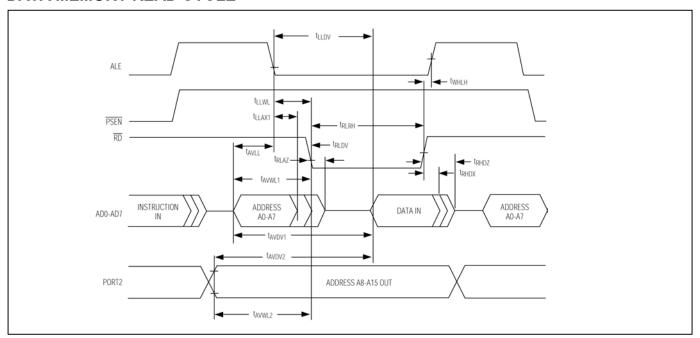

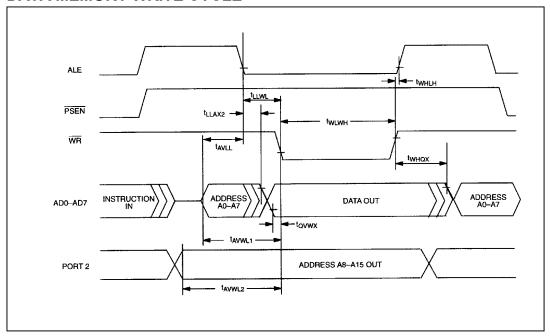

The DS80C320/DS80C323 address memory in an identical fashion to the standard 80C32. Electrical timing appears different due to the high-speed nature of the product. However, the signals are essentially the same. Detailed timing diagrams are provided in the *Electrical Specifications* section.

This data sheet assumes the user is familiar with the basic features of the standard 80C32. In addition to these standard features, the DS80C320/DS80C323 include many new functions. This data sheet provides only a summary and overview. Detailed descriptions are available in the *High-Speed Microcontroller User's Guide*.

Figure 2. Comparative Timing of the DS80C320/DS80C323 and 80C32

#### **HIGH-SPEED OPERATION**

The DS80C320/DS80C323 are built around a high-speed, 80C32-compatible core. Higher speed comes not just from increasing the clock frequency but also from a newer, more efficient design.

In this updated core, dummy memory cycles have been eliminated. In a conventional 80C32, machine cycles are generated by dividing the clock frequency by 12. In the DS80C320/DS80C323, the same machine cycle is performed in 4 clocks. Thus the fastest instruction, one machine cycle, is executed three times faster for the same crystal frequency. Note that these are identical instructions. Figure 2 shows a comparison of the timing differences. The majority of instructions will see the full 3-to-1 speed improvement. Some instructions will get between 1.5X and 2.4X improvement. Note that all instructions are faster than the original 80C51. Table 1 shows a summary of the instruction set, including the speed.

The numerical average of all op codes is approximately a 2.5-to-1 speed improvement. Individual programs are affected differently, depending on the actual instructions used. Speed-sensitive applications would make the most use of instructions that are three times faster. However, the sheer number of 3-to-1 improved op codes makes dramatic speed improvements likely for any code. The Dual Data Pointer feature also allows the user to eliminate wasted instructions when moving blocks of memory.

#### INSTRUCTION SET SUMMARY

All instructions in the DS80C320/DS80C323 perform the same functions as their 80C32 counterparts. Their effect on bits, flags, and other status functions is identical. However, the timing of each instruction is different. This applies both in absolute and relative number of clocks.

For absolute timing of real-time events, the timing of software loops will need to be calculated using the Table 1. However, counter/timers default to run at the older 12 clocks per increment. Therefore, while software runs at higher speed, timer-based events need no modification to operate as before. Timers can be set to run at 4 clocks per increment cycle to take advantage of higher speed operation.

The relative time of two instructions might be different in the new architecture than it was previously. For example, in the original architecture, the "MOVX A, @DPTR" instruction and the "MOV direct, direct" instruction used two machine cycles or 24 oscillator cycles. Therefore, they required the same amount of time. In the DS80C320/DS80C323, the MOVX instruction can be done in two machine cycles or eight oscillator cycles, but the "MOV direct, direct" uses three machine cycles or 12 oscillator cycles. While both are faster than their original counterparts, they now have different execution times from each other. This is because in most cases, the DS80C320/DS80C323 use one cycle for each byte. The user concerned with precise program timing should examine the timing of each instruction for familiarity with the changes. Note that a machine cycle now requires just four clocks, and provides one ALE pulse per cycle. Many instructions require only one cycle, but some require five. In the original architecture, all were one or two cycles except for MUL and DIV.

**Table 1. Instruction Set Summary**

| SYMBOL | FUNCTION                                               |

|--------|--------------------------------------------------------|

| A      | Accumulator                                            |

| Rn     | Register R7 to R0                                      |

| direct | Internal Register Address                              |

| @Ri    | Internal Register pointed to by R0 or R1 (except MOVX) |

| rel    | Two's Complement Offset Byte                           |

| SYMBOL   | FUNCTION                   |

|----------|----------------------------|

| bit      | direct bit-address         |

| #data    | 8-bit constant             |

| #data 16 | 16-bit constant            |

| addr 16  | 16-bit destination address |

| addr 11  | 11-bit destination address |

| INSTRUCTION       | вуте     | OSCILLATOR<br>CYCLES | INSTRUCTION       | BYTE | OSCILLATOR<br>CYCLES |

|-------------------|----------|----------------------|-------------------|------|----------------------|

| ARITHMATIC INSTI  | RUCTIONS | S                    |                   | •    |                      |

| ADD A, Rn         | 1        | 4                    | INC A             | 1    | 4                    |

| ADD A, direct     | 2        | 8                    | INC Rn            | 1    | 4                    |

| ADD A, @Ri        | 1        | 4                    | INC direct        | 2    | 8                    |

| ADD A, #data      | 2        | 8                    | INC @Ri           | 1    | 4                    |

| ADDC A, Rn        | 1        | 4                    | INC DPTR          | 1    | 12                   |

| ADDC A, direct    | 2        | 8                    | DEC A             | 1    | 4                    |

| ADDC A, @Ri       | 1        | 4                    | DEC Rn            | 1    | 4                    |

| ADDC A, #data     | 2        | 8                    | DEC direct        | 2    | 8                    |

| SUBB A, Rn        | 1        | 4                    | DEC @Ri           | 1    | 4                    |

| SUBB A, direct    | 2        | 8                    | MUL AB            | 1    | 20                   |

| SUBB A, @Ri       | 1        | 4                    | DIV AB            | 1    | 20                   |

| SUBB A, #data     | 2        | 8                    | DA A              | 1    | 4                    |

| LOGICAL INSTRUC   | TIONS    |                      |                   |      |                      |

| ANL A, Rn         | 1        | 4                    | XRL A, Rn         | 1    | 4                    |

| ANL A, direct     | 2        | 8                    | XRL A, direct     | 2    | 8                    |

| ANL A, @Ri        | 1        | 4                    | XRL A, @Ri        | 1    | 4                    |

| ANL A, #data      | 2        | 8                    | XRL A, #data      | 2    | 8                    |

| ANL direct, A     | 2        | 8                    | XRL direct, A     | 2    | 8                    |

| ANL direct, #data | 3        | 12                   | XRL direct, #data | 3    | 12                   |

| ORL A, Rn         | 1        | 4                    | CLR A             | 1    | 4                    |

| ORL A, direct     | 2        | 8                    | CPL A             | 1    | 4                    |

| ORL A, @Ri        | 1        | 4                    | RL A              | 1    | 4                    |

| ORL A, #data      | 2        | 8                    | RLC A             | 1    | 4                    |

| ORL direct, A     | 2        | 8                    | RR A              | 1    | 4                    |

| ORL direct, #data | 3        | 12                   | RRC A             | 1    | 4                    |

**Table 1. Instruction Set Summary (continued)**

| INSTRUCTION          | BYTE     | OSCILLATOR<br>CYCLES | INSTRUCTION         | BYTE | OSCILLATOR<br>CYCLES |

|----------------------|----------|----------------------|---------------------|------|----------------------|

| DATA TRANSFER INS    | STRUCTI  | ONS                  |                     |      |                      |

| MOV A, Rn            | 1        | 4                    | MOVC A,<br>@A+DPTR  | 1    | 12                   |

| MOV A, direct        | 2        | 8                    | MOVC A, @A+PC       | 1    | 12                   |

| MOV A, @Ri           | 1        | 4                    | MOVX A, @Ri         | 1    | 8-36*                |

| MOV A, #data         | 2        | 8                    | MOVX A, @DPTR       | 1    | 8-36*                |

| MOV Rn, A            | 1        | 4                    | MOVX @Ri, A         | 1    | 8-36*                |

| MOV Rn, direct       | 2        | 8                    | MOVX @DPTR, A       | 1    | 8-36*                |

| MOV Rn, #data        | 2        | 8                    | PUSH direct         | 2    | 8                    |

| MOV direct, A        | 2        | 8                    | POP direct          | 2    | 8                    |

| MOV direct, Rn       | 2        | 8                    | XCH A, Rn           | 1    | 4                    |

| MOV direct1, direct2 | 3        | 12                   | XCH A, direct       | 2    | 8                    |

| MOV direct, @Ri      | 2        | 8                    | XCH A, @Ri          | 1    | 4                    |

| MOV direct, #data    | 3        | 12                   | XCHD A, @Ri         | 1    | 4                    |

| MOV @Ri, A           | 1        | 4                    | , ,                 |      |                      |

| MOV @Ri, direct      | 2        | 8                    |                     |      |                      |

| MOV @Ri, #data       | 2        | 8                    |                     |      |                      |

| MOV DPTR, #data 16   | 3        | 12                   |                     |      |                      |

| BIT MANIPULATION     | INSTRU   | CTIONS               |                     |      |                      |

| CLR C                | 1        | 4                    | ANL C, bit          | 2    | 8                    |

| CLR bit              | 2        | 8                    | ANL C, bit          | 2    | 8                    |

| SETB C               | 1        | 4                    | ORL C, bit          | 2    | 8                    |

| SETB bit             | 2        | 8                    | ORL C, bit          | 2    | 8                    |

| CPL C                | 1        | 4                    | MOV C, bit          | 2    | 8                    |

| CPL bit              | 2        | 8                    | MOV bit, C          | 2    | 8                    |

| PROGRAM BRANCH       | ING INST | RUCTIONS             | ,                   | 1    |                      |

| ACALL addr 11        | 2        | 12                   | CJNE A, direct, rel | 3    | 16                   |

| LCALL addr 16        | 3        | 16                   | CJNE A, #data, rel  | 3    | 16                   |

| RET                  | 1        | 16                   | CJNE Rn, #data, rel | 3    | 16                   |

| RETI                 | 1        | 16                   | CJNE Ri, #data, rel | 3    | 16                   |

| AJMP addr 11         | 2        | 12                   | NOP                 | 1    | 4                    |

| LJMP addr 16         | 3        | 16                   | JC rel              | 2    | 12                   |

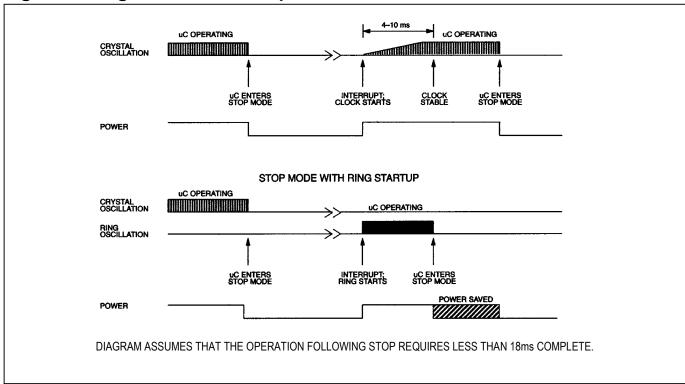

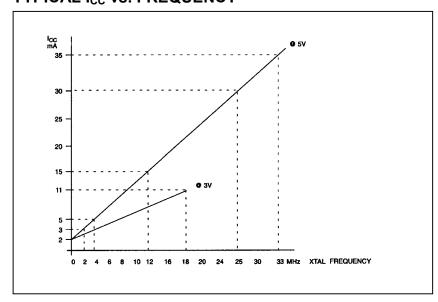

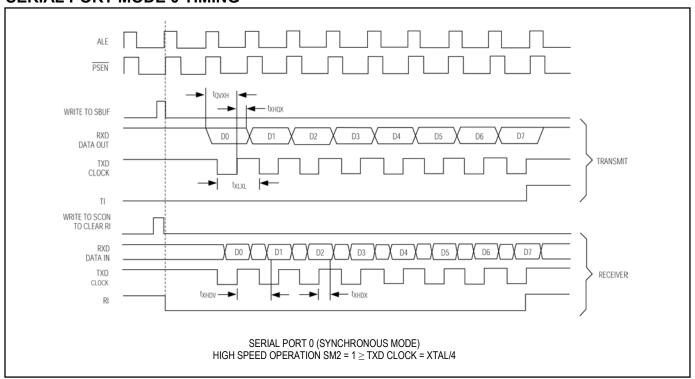

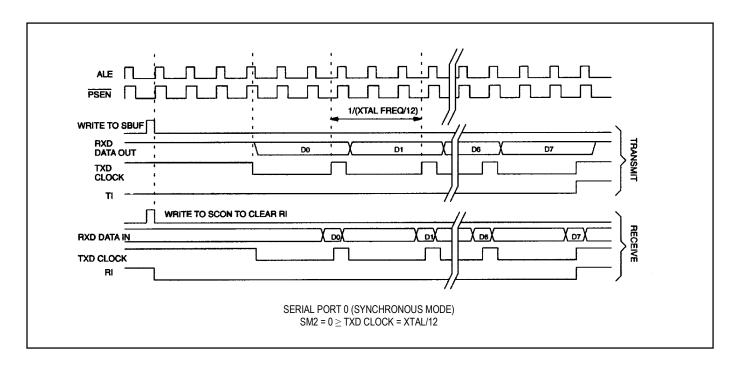

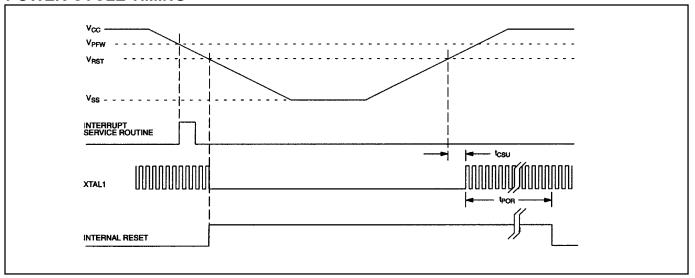

| SJMP rel             | 2        | 12                   | JNC rel             | 2    | 12                   |